如果你问十位不同的工程师他们会如何设计人工智能加速器,你会得到十种不同的方案,来排列现代尖端芯片上数十亿个晶体管。有了像戴夫·迪泽尔(Dave Ditzel)这样拥有丰富 CPU 设计经验的专家领导这个项目,Esperanto Technologies 的机器学习芯片设计必然会涉及到 CPU 也就不足为奇了。如果一个定制 CPU 还不够,那两个设计方案又如何呢?Esperanto 在近 240 亿个晶体管的预算下,成功地将近 1100 个晶体管集成到了他们的首款人工智能加速器——ET-SoC-1 上。

ET-SoC-1(全称为“Esperanto Technologies Supercomputer-on-Chip 1”)面向超大规模数据中心市场,是 Esperanto 全新人工智能加速器系列的首款产品。ET-SoC-1 是一款推理加速器,而非训练加速器。虽然设计已经完成,但截至今年年初,该公司尚未看到首颗芯片。我们最初讨论 Esperanto 结束隐身模式时,预计时间大约在 2020 年左右。显然,开发进度有所延误,如果新的时间表保持不变,芯片应该会在本季度恢复生产,并有望在 2022 年初实现量产。考虑到其他人工智能初创公司已经拥有超过一年的量产芯片样品,两年的延迟无疑代价高昂。尽管如此,Esperanto 终于准备好分享这款新芯片的技术细节。值得一提的是,Dave Ditzel 将在即将于 8 月举行的 Hot Chips 33 大会上展示 ET-SoC-1。

Esperanto Technologies 首席执行官 Art Swift 做出了一些初步的性能预测。Swift 表示:“我们预计在推荐网络等关键工作负载上,性能将提升高达 50 倍,在图像分类方面,性能将提升高达 30 倍。” 这些预测是基于 ET-SoC-1 的全芯片仿真,并与“数据中心现有竞争对手”的推理基准测试结果进行比较得出的。“但或许更令人兴奋、更重要的是我们能够实现的能效。我们预计,就每瓦推理次数而言,我们的能效将比现有解决方案高出 100 倍。” 他补充道。这些过于宽泛的性能预测需要谨慎对待,但 Esperanto 表示,我们可以在不久的将来看到已发布的芯片特性测试结果。

模块化平铺设计

Esperanto 采用基于分块架构的非常规范的设计。该芯片使用公司自主设计的符合 RISC-V 规范的 CPU 内核,采用标准的 DDR4 内存和传统的内存层次结构,并充分利用了所有可用的 RISC-V 软件生态系统。换句话说,实际上,ET-SoC-1 可以作为标准的 RISC-V 服务器 CPU 通过“鸭子测试”(Duck Test),尽管它包含大量简单的内核,在通用工作负载下性能可能不太理想。事实上,Esperanto 认为正因如此,他们的解决方案才具有很强的未来适应性。该公司表示,通过集成大量 CPU,其核心数量可以从数百个扩展到数千个。实际上,由于 ET-SoC-1 是为数据中心设计的,对于边缘推理等低功耗应用,我们或许可以期待一个功能类似的精简版 ET-SoC-1。 Esperanto 最初在非常宏观的层面上谈论他们的设计时,设想的芯片核心数量将是本文将要讨论的 ET-SoC-1 的四倍。如果他们的设计最终被证明是可行的,那么 Esperanto 完全有能力将 ET-SoC-1 向这个方向扩展。

自定义内核

Esperanto 选择了 RISC-V 架构。他们设计了两个定制内核——ET-Minion 和 ET-Maxion。顾名思义,ET-Maxion 是一款典型的大核心设计,能够运行 Linux 等标准操作系统。同样,ET-Minion 是一款功能强大的小型 CPU,带有定制的张量扩展,用于处理矩阵乘法等运算。在 ET-SoC-1 系统中,ET-Maxion 用作控制 CPU,而 ET-Minion 则负责繁重的数据处理。

ET-Maxion

正如我们之前提到的,ET-Maxion 是一款定制的高性能大核心设计。它专为台积电的 7nm 工艺打造,频率超过 2GHz。ET-Maxion 实际上是加州大学伯克利分校乱序执行机器 (BOOM) v2 CPU 的一个分支,但为了使其更具竞争力并达到商业级品质,它进行了大量的改进和升级,以至于现在两者之间的渊源几乎难以辨认。事实上,BOOM 的开发者 Chris Celio 后来加入了 Esperanto 公司,参与 ET-Maxion 的开发(尽管他自 2020 年起加入了英特尔担任 CPU 架构师)。与 BOOM 相比,ET-Maxion 对机器的各个方面都进行了改进。它的宽度、长度和体积都显著增加。整个前端都经过了重新设计,各种执行单元也进行了重新架构。它配备了全新的、最先进的分支预测器和预取器。此外,它还采用了全新的、从零开始设计的缓存和 TLB,并支持 ECC 纠错。最后,Esperanto 还增加了商用级的硅调试和性能监控功能。就性能而言,ET-Maxion 在 SPEC2006 的 ISO 频率下据称略逊于 Cortex-A72,但优于 Cortex-A57。在 SiFive 最近发布 P550 内核之前,ET-Maxion 很可能是 RISC-V 领域性能最高的内核。SiFive 最近推出了 P550 内核,据称其 SPECInt 2006 得分达到 8.65/GHz,在 IPC 方面显著优于 ET-Maxion(以及 A72)。

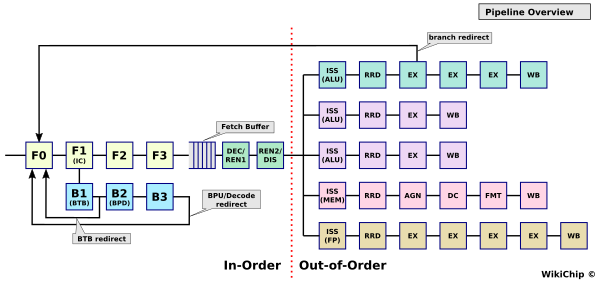

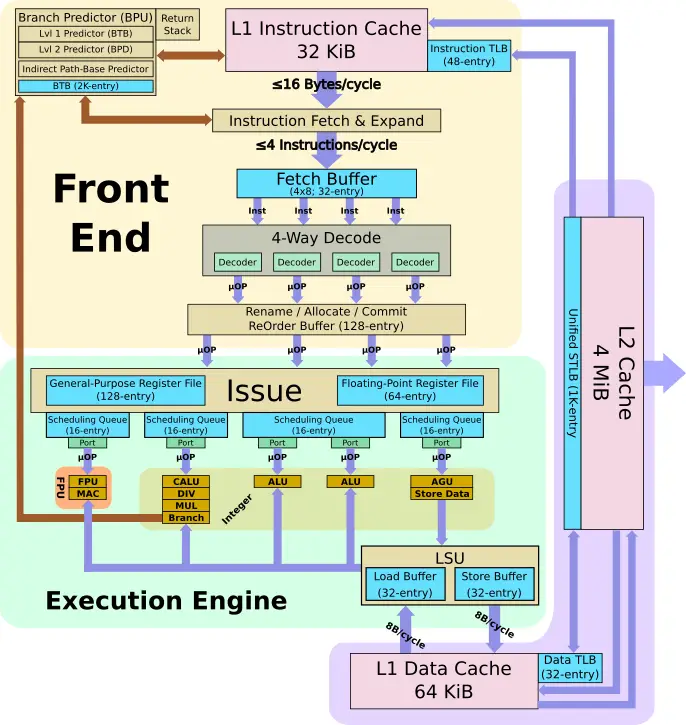

ET-Maxion 是一款乱序执行的 CPU 内核,采用 10 级流水线。该内核为四宽机器,每个周期能够获取 16 字节数据,对其进行解码,并以每周期 4 条指令的速率将其分发到后端。指令从一个 32 KiB 的分块指令缓存中获取,该缓存支持奇偶校验和 ECC 纠错。Esperanto 公司表示,他们投入了大量精力开发了一种全新的、最先进的条件预测器和一个基于路径的间接预测器,并由一个 2K 条目的压缩 BTB 提供支持。分支预测器由两级预测器组成。一个快速的、单周期的、基于 BTB 的预测器执行初始猜测,然后由第二级、速度较慢的多周期、高精度分支预测器进行验证,该预测器可能会覆盖初始猜测。

每个周期最多可以向调度器分派四条指令。ET-Maxion 采用分布式调度器设计,总容量为 64 个调度器条目。其中,LSU、FPU、复杂 ALU 和简单 ALU 各有一个调度器。需要注意的是,这里有两个简单 ALU,而复杂 ALU 单元也能够处理分支操作。

执行单元由一个 64 项浮点物理寄存器文件和一个 128 项整数物理寄存器文件提供数据。在执行单元方面,机器采用五宽架构,其中两个简单的整数单元位于同一个调度器上。每个周期最多可以调度五条指令执行。浮点单元为 64 位宽,并完全支持 RISC-V 的 32 位 (F) 和 64 位 (D) 浮点扩展。总体而言,核心的执行能力受限于其 128 项重排序缓冲区,与机器前端一样,该缓冲区每个周期最多可以处理四条指令。

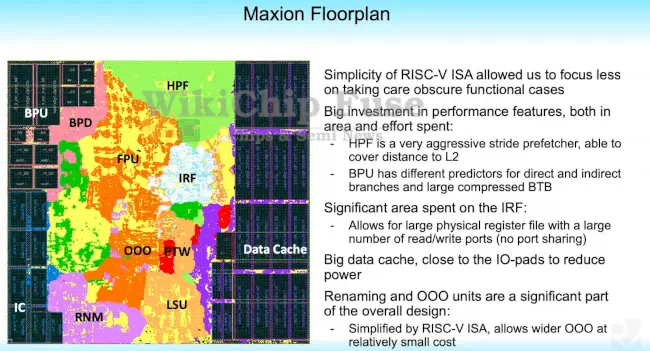

Esperanto 最初考虑过定制指令集架构 (ISA),但最终还是选择了 RISC-V,因为它更简单。该公司解释说,这种简单的架构让他们能够将更多精力集中在性能特性上,而不是费力地去解决其他 ISA 的各种特殊情况和怪癖。ET-Maxion 的平面图如下所示。请注意,图中显示的是核心部分,没有 L2 缓存。从芯片布局图可以看出,缓存阵列(几乎占总面积的 1/3)和分支预测单元占据了相当大的面积。核心顶部是硬件预取器 (HPF)(仅支持 L1 缓存),与其他组件相比,它的体积非常大。选择更激进(速度更慢但精度更高)

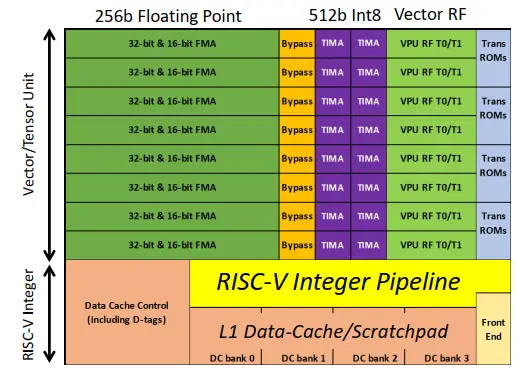

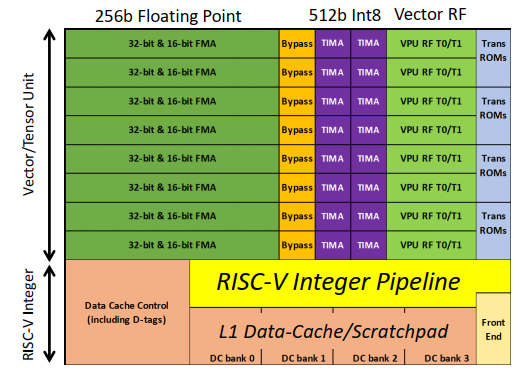

件(即每个线程总共 64 项)。浮点向量单元被细分为 8 个 32 位 FMA,每个 FMA 最多可以执行 16 SP FLOPs/周期或 32 HF FLOPs/周期。整数向量单元的宽度为 512 位,是浮点向量单元的两倍。该单元被细分为 16×32 位 TIMA,每个 TIMA 每个周期最多可执行 128 个 INT8 操作。虽然浮点向量单元可以从浮点向量寄存器文件获取数据,但宽度是其两倍的整数向量单元需要从浮点向量寄存器文件中提取一半向量(256 位),并从其自身的私有整数寄存器文件(256 位)中提取另一半向量,才能得到总宽度为 512 的向量。

Esperanto 在 ET-Minion 中集成了强大的浮点运算能力,这与其他当代加速器形成了鲜明对比。通常我们看到的加速器仅提供 INT8 运算。虽然 8 位量化也能提供相当不错的精度,但 Esperanto 在需要 FP16(或 FP32)运算的工作负载方面更具优势。

除了向量单元之外,ET-Minion 还集成了一个向量超越单元,它可以执行各种三角函数、指数函数和对数函数等超越函数运算,从而加速诸如激活函数之类的计算。该超越单元基于 ROM,相比硅芯片而言,功耗更低。这里的向量单元还有一些其他的细微差别。除了标准的 RISC-V 指令之外,Esperanto 还实现了自己的指令扩展——两个。他们添加了多周期张量指令和相应的向量超越指令。一些读者可能会对此感到不安,尤其是在 Esperanto 如此大力宣传 RISC-V 的优势之后。但事实是,RISC-V 与所有其他指令集架构 (ISA) 一样,没有任何专门用于加速 AI 的指令,因此这些扩展是必要的。事实上,RISC-V 基金会预见到了这一点,并将自定义扩展直接嵌入到规范中,这就是为什么世界语能够以标准方式实现这一点的原因。目前尚不清楚世界语是否会公开其扩展,或者他们是否打算将其保持专有状态,因为这与他们声称的面向未来相悖。

多周期张量指令允许核心读取单条指令,并通过张量序列器状态机,在数百甚至数千个周期内重放一系列操作。与大多数序列器一样,ET-Min

进一步,没有采用台积电的标准 SRAM 产品,而是自行设计了定制的 SRAM。虽然单元尺寸更大,但可以在远低于标称电压的电压下稳定工作。“我所说的低电压工作,是指远低于标称电压的工作电压。例如,如果标称电压是 0.75V 左右,那么我们的工作电压大约是 400mV,”Swift 说道。

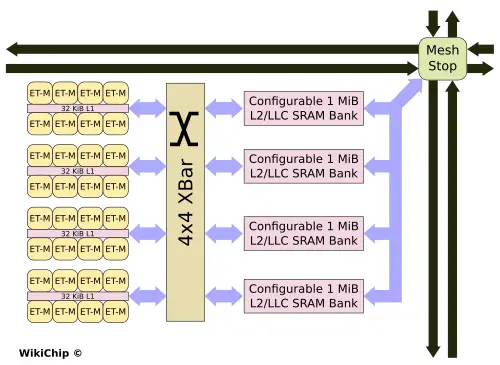

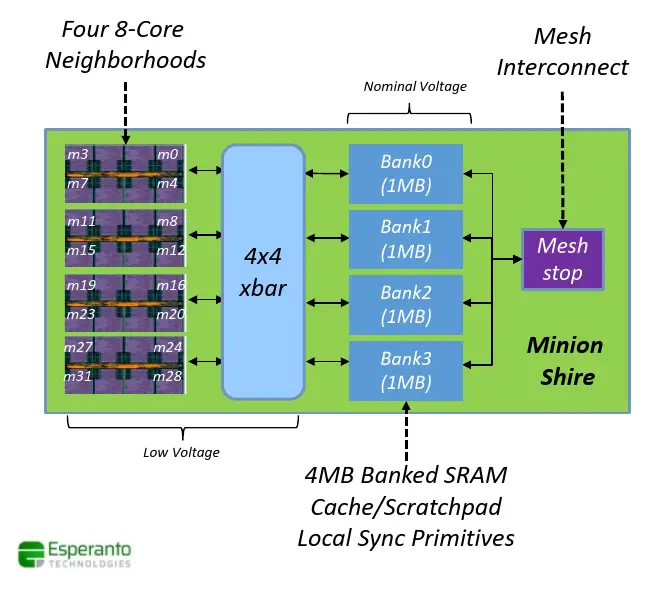

Minion 计算阵列

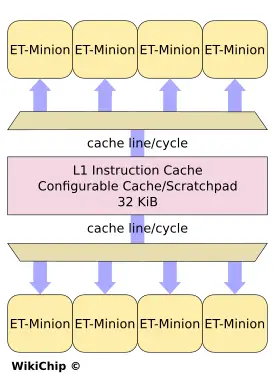

将八个 ET-Minion 分组,就形成了 Esperanto 所说的 Minion 邻域。在邻域内,每个核心竞争性地共享指令缓存。缓存容量为 32 KiB。每个周期,一条缓存行会被发送到两个核心。换句话说,指令缓存会在每个周期轮询一对核心,将 64B(相当于 16 条指令)的数据发送到两个不同的核心。核心会缓存这条缓存行,以便在指令缓存继续向其他核心提供数据时,它们能够继续运行。

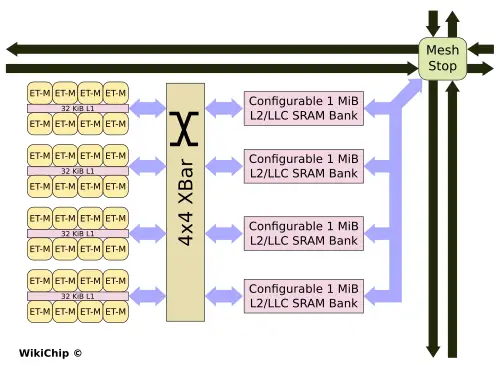

Minion 核心组

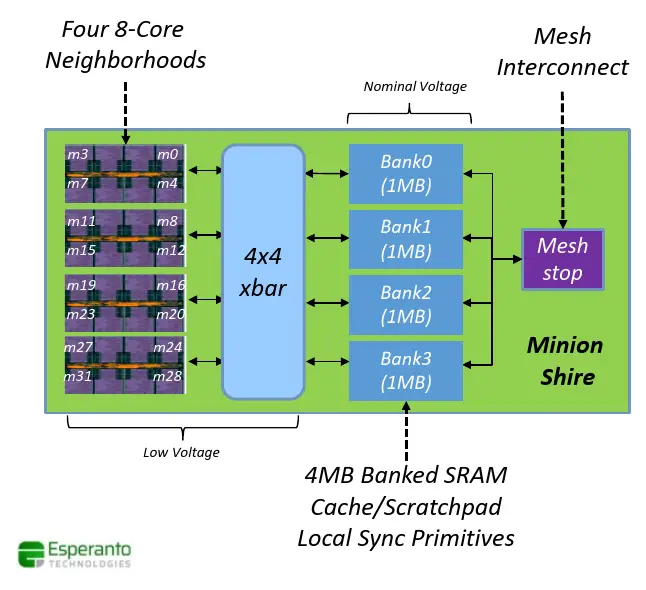

四个社区被组合成一个 Minion Shire,总共包含 32 个核心。每个八核社区通过交叉开关连接到四个 L2 内存库。L2 内存由四个 1 MiB 的 SRAM 库组成,可通过软件配置为缓存或暂存内存。在暂存内存配置下,整个内存是一个大的地址空间,软件可以利用该地址空间以精确的方式组织数据并进行访问。值得注意的是,默认情况下每个 Minion Shire 都拥有私有的 L2 缓存,但它也可以配置为覆盖整个芯片的末级缓存。所有这些功能都是以库为单位进行配置的。例如,一个库可以保留为暂存内存,另一个库用于 1 MiB/Shire 的 LLC(末级缓存),而另外两个库可以配置为 2 MiB 的私有 L2 缓存。每个 Shire 都可以通过网状互连与其他 Shire 通信,每个 Minion Shire 对应一个网状互连节点。

由于 ET-Minion 采用低压设计,其各个单元以及交叉开关位于 Shire 内部独立的低压电源层上。Shire 的其余部分(例如,分组式 SRAM 和网状互连组件)则位于标准电压层上。

模块化平铺架构

芯片的芯片设计简洁明了,每个 Minion Shire 都通过网状连接点与其他 Shire 以及芯片上的任何其他组件相连。网状连接点在四个基本方向上各包含两条单向链路。这些链路的宽度似乎均为 1024 字节。Esperanto 在芯片上还有一些额外的组件,例如内存通道和 PCIe 接口,它们也通过各自的网状连接点连接到整个网状互连网络中。

ET-SoC-1

这一切最终引出了 Esperanto 的首款产品——ET-SoC-1。这款芯片集成了 34 个 Minion Shire,呈 6×6 网格排列。网格上的另外两个单元分别用于控制处理器集群和 PCIe 单元。34 个 Minion Shire 意味着芯片上共有 1088 个 ET-Minion 处理器以及 136 MiB 可配置的 L2 内存。此外,还有一个独立的 ET-Mini

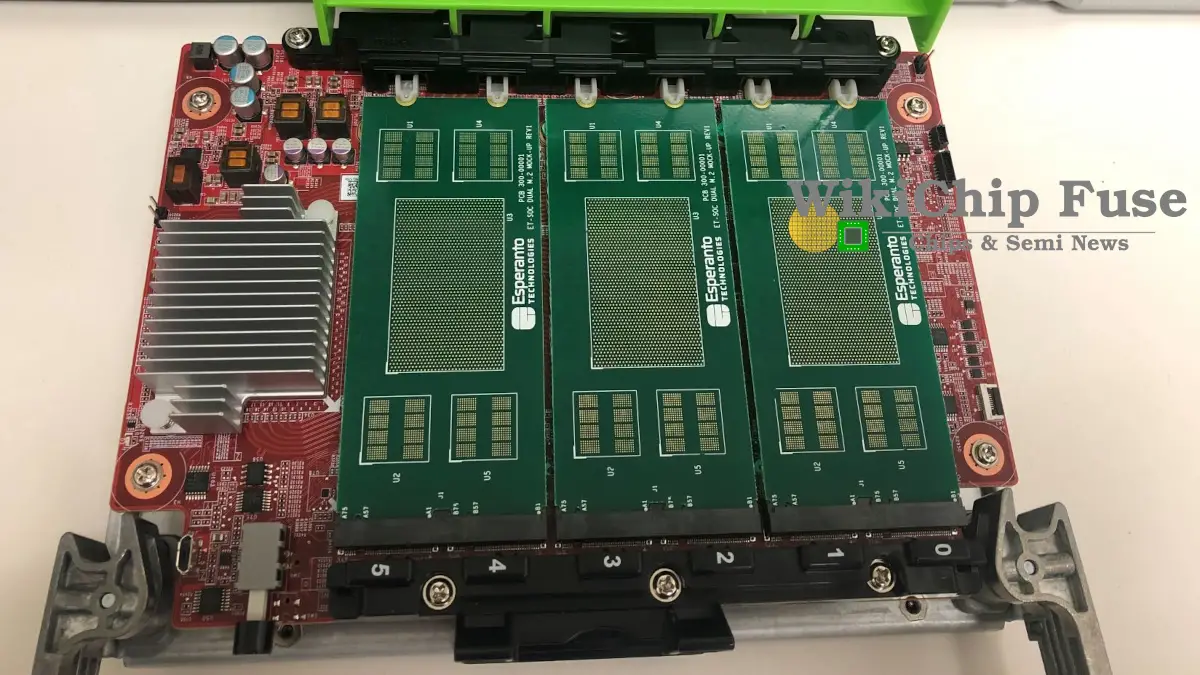

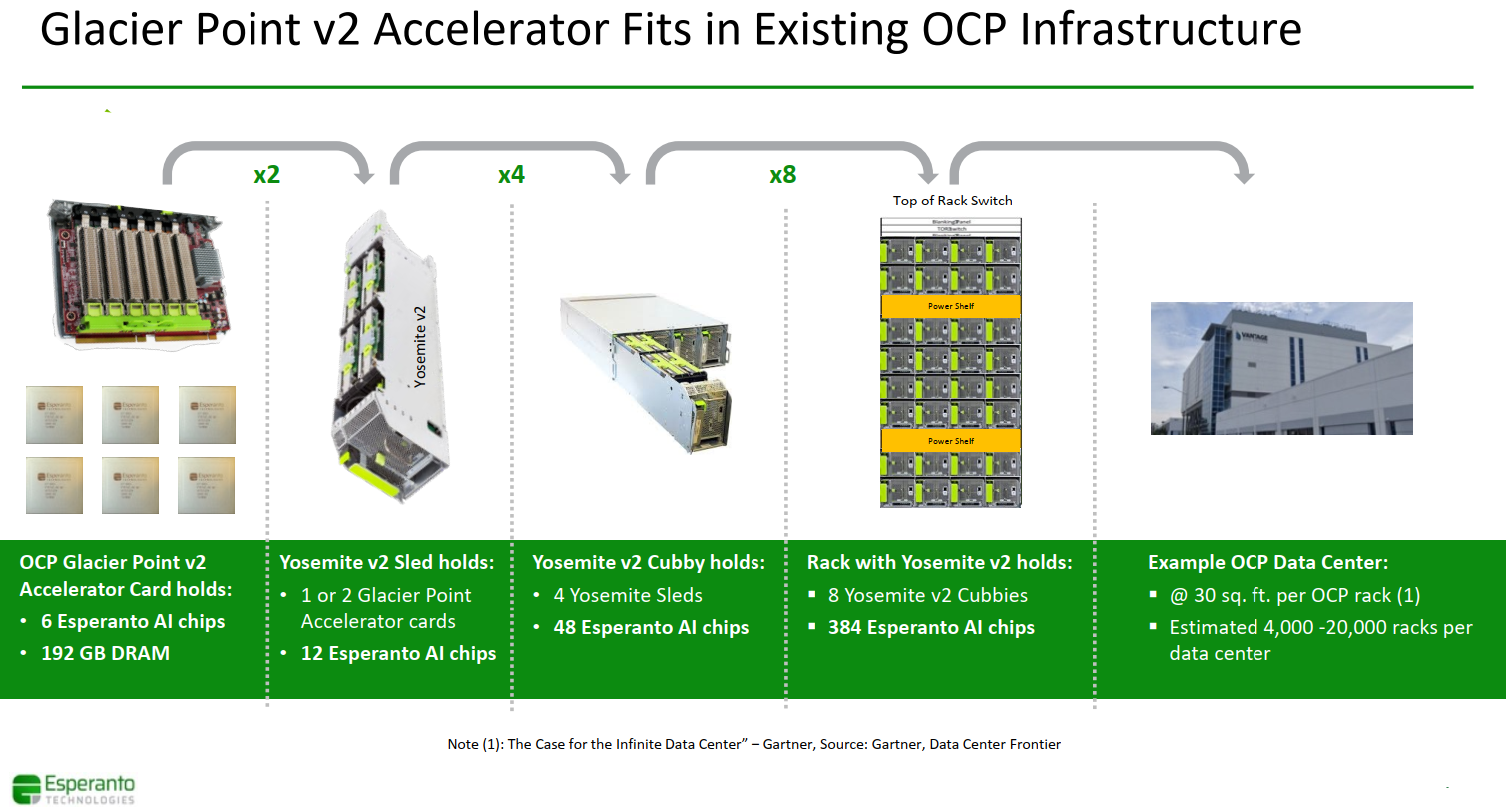

规格要求。我们也期待未来能够推出更高功率的 PCIe 扩展卡。

从物理层面来说,该芯片采用台积电的 N7 工艺制造。Esperanto 并未透露芯片尺寸,但考虑到其集成了 238 亿个晶体管,其面积很可能超过 350 平方毫米。虽然其标称频率可达 1.5GHz,但为了实现 20W 的功耗目标,该芯片的目标频率约为 1GHz。单个 ET-Minion 在 1GHz 频率下能够达到 128 OPS(INT8

点服务器平台。六个模块集成后,每张 Glacier Point 卡将拥有 6,558 个 RISC-V 核心,以及 192 GiB LPDDR4x 内存,DRAM 带宽为 822 GB/s。理论上,该卡的峰值性能可达 835.6 TOPS(INT8)或接近 210 teraFLOPS(半精度)。

评论区