在日本举行的 2019 年超大规模集成电路研讨会结束后,台积电举行了一场小型新闻发布会。此外,台积电还在 2019 年西部半导体展(SEMICON West 2019)上发表了封装方面的演讲。本文是对这两项活动的总结。

N7

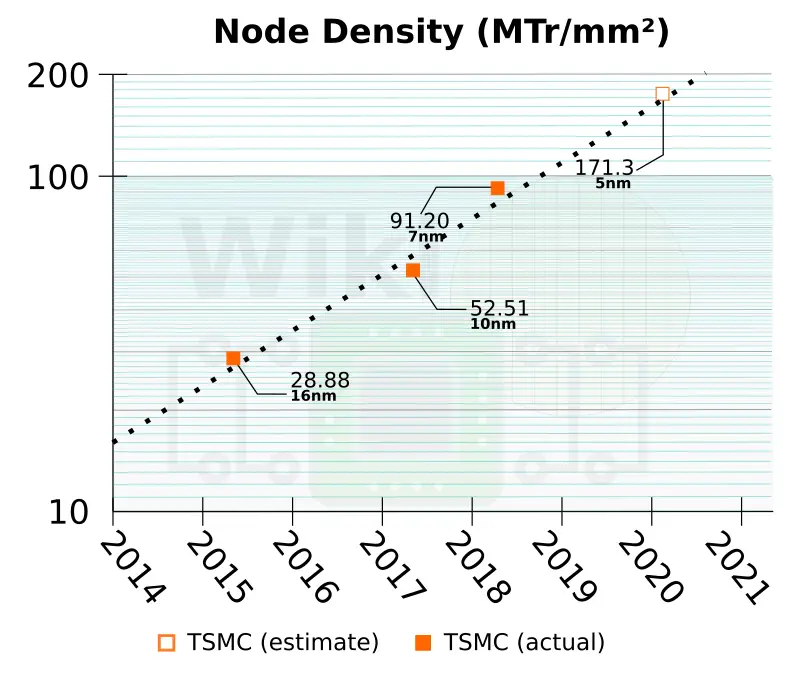

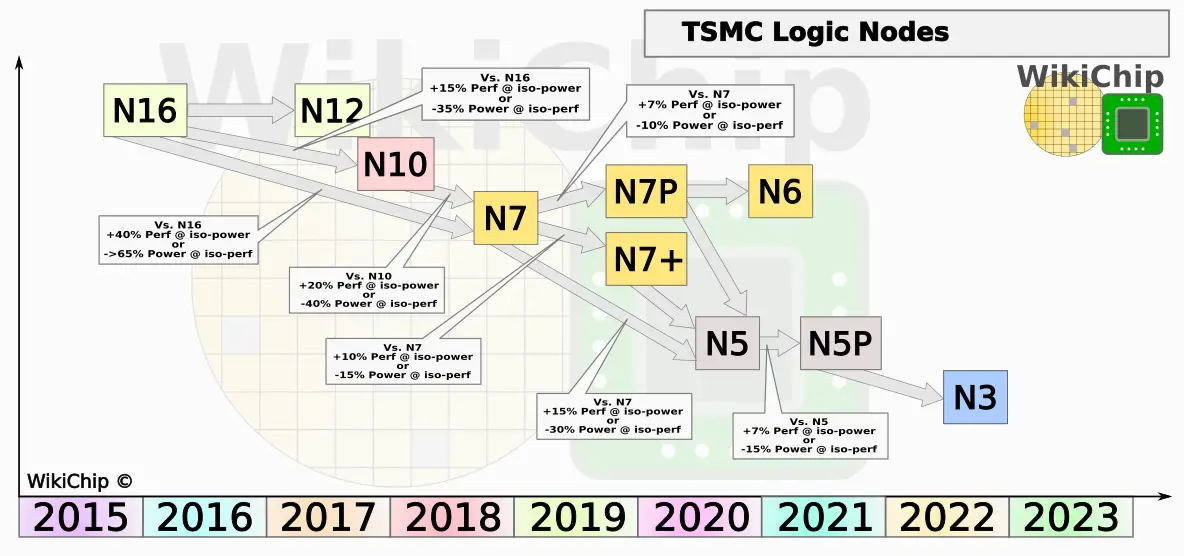

台积电认为其 7 纳米制程(N7)是目前出货的最先进的逻辑技术。WikiChip 也基本认同这一观点。在最近的超大规模集成电路研讨会上,台积电与他人合著了一篇关于其 7 纳米制程的论文 ,我们此前也报道过该论文,其中详细阐述了设计规则。除了少数几家关键的领先客户外,据说大多数台积电客户都是直接从 N16 制程过渡到 N7 制程。他们的 N10 制程被认为是一个短期使用的制程,主要用于良率学习。从 N16 制程过渡到 N7 制程,N7 制程可提供 3.3 倍的布线门密度,以及约 35-40%的速度提升或 65%的功耗降低。

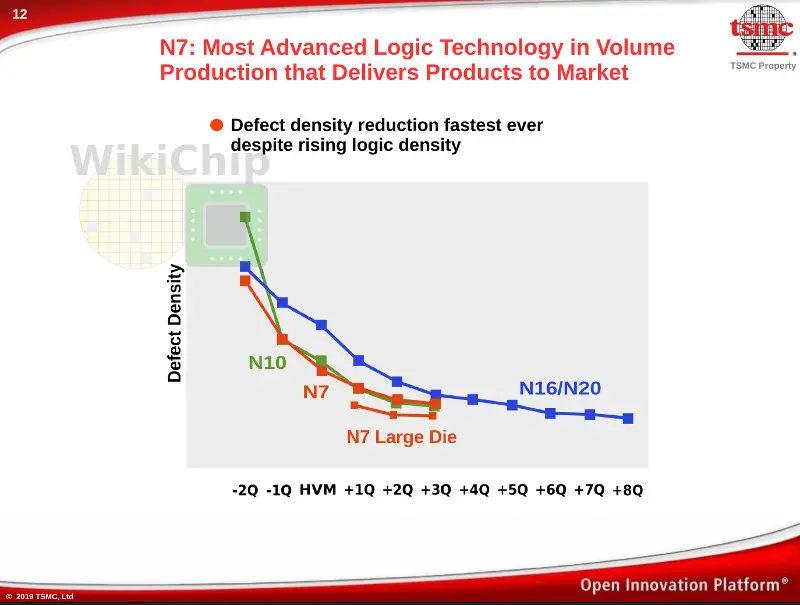

台积电 N7 工艺的一大亮点是其缺陷密度。台积电表示,吸取了 N10 工艺的经验,N7 工艺的缺陷密度下降速度创历史新高,并最终稳定在与前代工艺相当的水平。随着台积电大力进军高性能计算(HPC)领域,他们开始分别报告芯片面积为 250 平方毫米及以上的移动客户和 HPC 客户的缺陷密度。

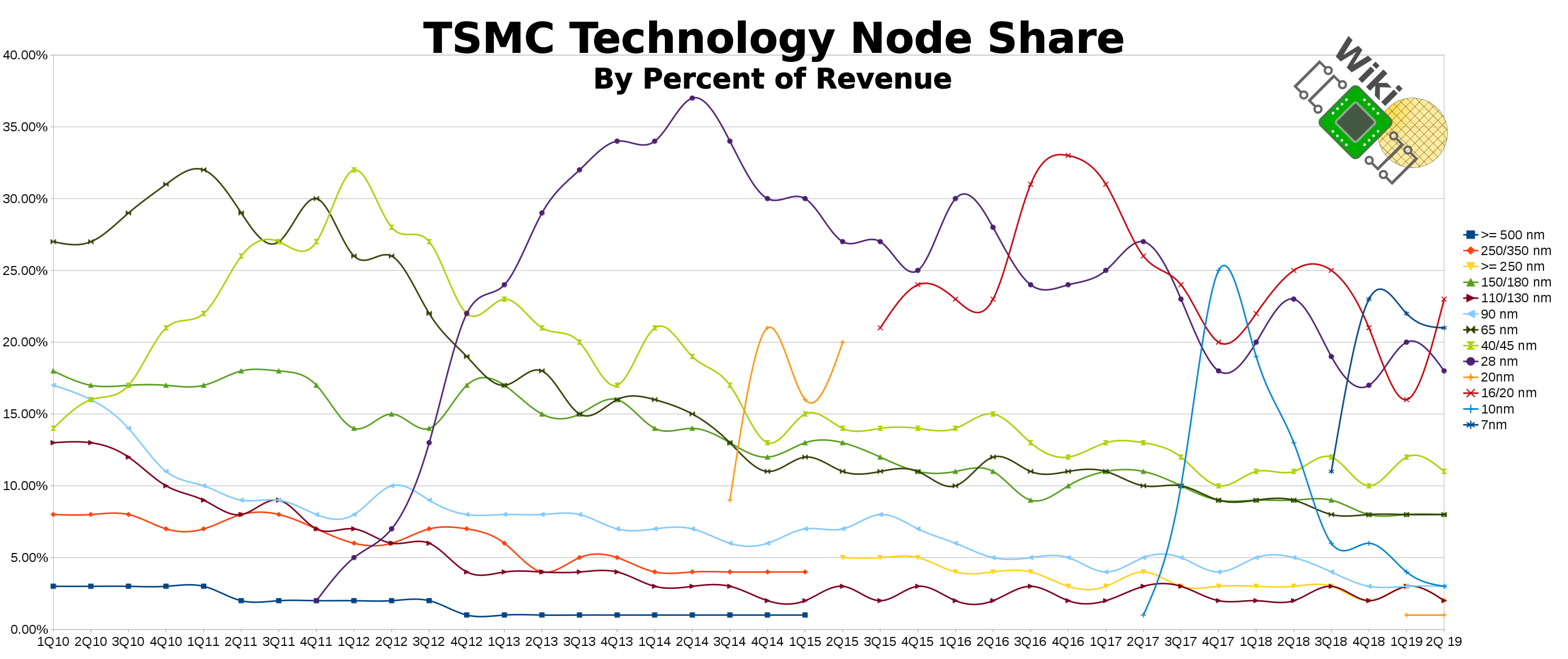

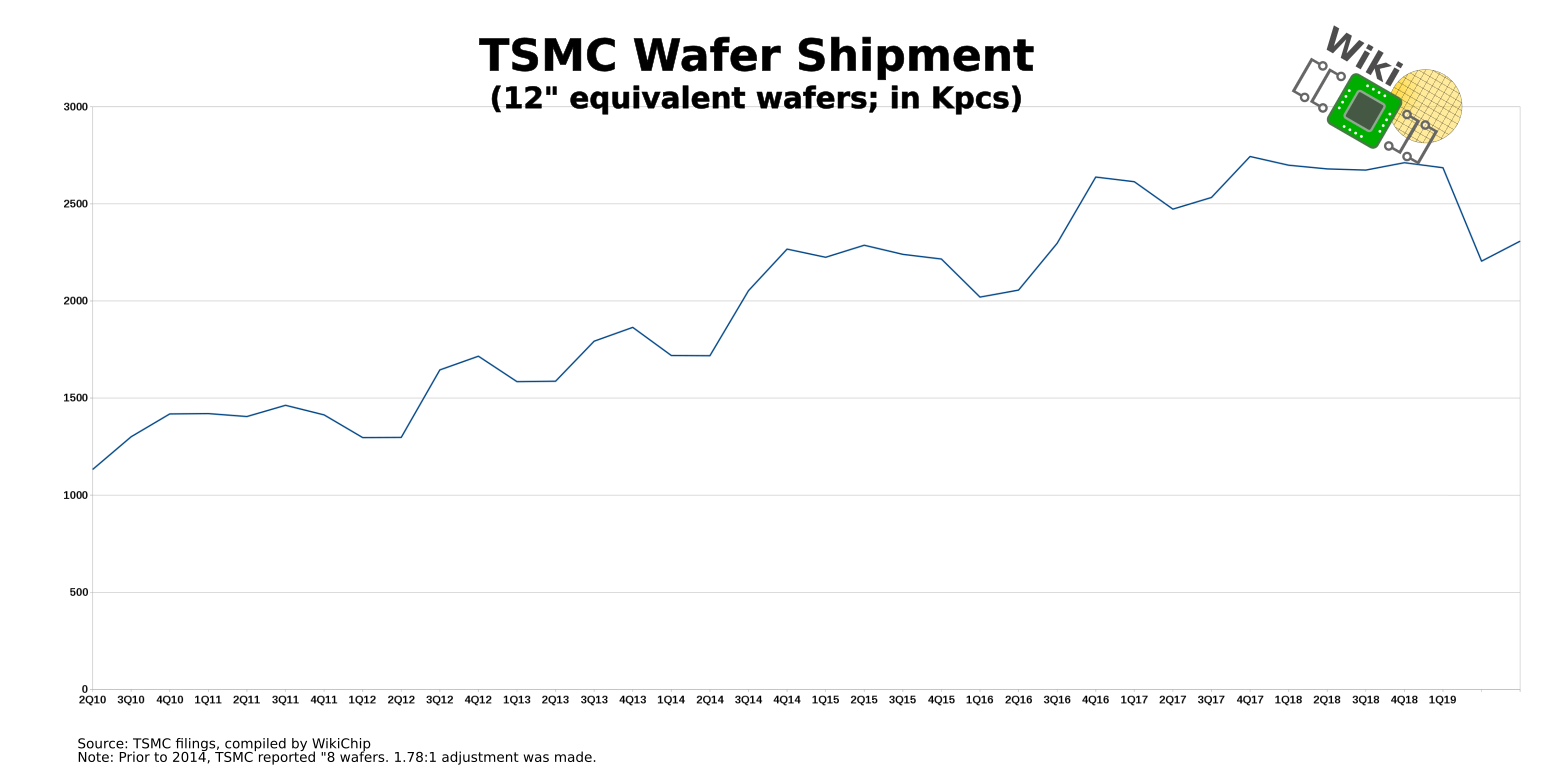

台积电7纳米制程的需求在过去半年环比略有下降,降幅约为1%。其营收的大部分仍然来自非常成熟的16纳米制程。第二季度晶圆出货量略有增长,但这符合第二季度的预期。与长期趋势相比,这实际上是三年来第二季度出货量的最低值。尽管如此,他们仍然相信7纳米制程全年营收将占到总营收的25%。

N7P

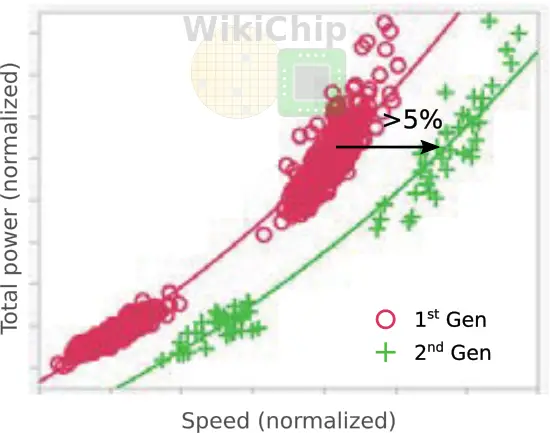

台积电已开始推出其 N7 工艺的优化版本,称为 N7 性能增强版(N7P) 。该工艺还有其他一些名称,例如“第二代 7 纳米”和“7 纳米第二年”。请勿将此工艺与 N7+混淆。N7P 是一种基于深紫外光刻(DUV)技术的优化工艺,采用相同的设计规则,并与 N7 完全兼容。N7P 引入了前端工艺(FEOL)和中端工艺(MOL)的优化,据称可在相同功耗下实现 7%的性能提升,或在相同速度下实现高达 10%的功耗降低。

N7+

台积电的 N7+工艺是其首个在关键层采用 EUV 光刻技术的工艺。N7+已于上季度(第二季度)投入量产。台积电表示,其良率与 N7 工艺相当。与 N7 工艺相比,N7+工艺的密度提升约 1.2 倍。据称,N7+工艺在相同功耗下可实现更高的性能(提升 10%),或者在相同性能下功耗降低高达 15%。从理论上看,N7+似乎略优于 N7P。但需要注意的是,这些改进只能通过全新的物理结构和新的 EUV 光刻掩模来实现。

N6

N6 是 N7 的 EUV 版本。它计划使用比 N7+ 更多的 EUV 层。N6 在设计规则和 IP 方面均与 N7 兼容,并将成为大多数客户的主要升级路径。N7 设计可以利用 EUV 光刻掩模和精度提升,在 N6 上重新流片;或者重新实现,以利用多晶硅扩散边缘 (PODE) 和连续扩散 (CNOD) 标准单元对接规则,据称这些规则可额外提高 18% 的密度。值得一提的是,N6 的独特之处在于它将于明年初进入风险生产阶段,并在 2020 年底前实现量产。这意味着它将在 N5 之后量产。因此,台积电表示,N6 融合了 N7+ 和 N5 EUV 的经验。

N5

台积电的 5 纳米工艺是继 N7 之后的下一个“完整节点”。N5 工艺已于今年第一季度进入风险生产阶段,预计将于 2020 年上半年实现量产。台积电表示,目前已有多个芯片流片工作正在进行中。N5 工艺在“多层”应用了极紫外光刻(EUV)技术。台积电已展示了极高的良率,并表示其在初始产品交付量(D0)方面与 N7 工艺的发展轨迹相似。N5 工艺被规划为一个长期应用的节点,预计其营收增长速度将超过 N7 工艺。

与 N7 相比,N5 的逻辑布线密度据称提高了 1.8 倍。在性能方面,N5 在相同功耗下性能提升 15%,或在相同性能下功耗降低 30%。与 N7 一样,N5 也将提供两种版本——移动应用版和高性能计算 (HPC) 版。HPC 单元将提供额外的性能提升选项,最高可达 N7 的 25%。

据我们估计,台积电将于明年初开始量产,届时其“完整节点”将领先于英特尔和三星。

N5P

与 7 纳米工艺一样,台积电将推出其 N5 工艺的优化版本,称为 N5 性能增强版(N5P)。该工艺采用相同的设计规则,并与 N5 完全兼容。通过前端工艺(FEOL)和中端工艺(MOL)的优化,N5P 在相同功耗下性能将比 N5 提升 7%,或在相同性能下功耗降低 15%。台积电对 N5P 的具体时间表尚未给出明确信息,但暗示可能会在 2020 年底或 2021 年初推出

N3

台积电表示其 3 纳米制程进展顺利,预计将于 2022 年左右推出 N3 工艺。虽然台积电此前曾将 GAA 视为 FinFET 的潜在继任者,但台积电和英特尔都认为,目前制造工艺更为简便的 FinFET,其性能提升空间足以满足下一制程的需求。我们目前认为,台积电在 N3 工艺中可能会继续采用 FinFET,但在后续制程节点中会转向 GAA。

评论区